# **Tektronix**

半导体材料与器件科学云讲堂

——半导体器件可靠性HCI/NBTI测试

主讲人: 王瑞恒——半导体领域测试专家

2020/9/14

#### 半导体材料与器件科学云讲堂

- ✓ 专业测试平台

- ✓ 六大类测试流程

- ✓ 剖析、解决半导体新问题

关注"泰克科技"服务号

#### 每月2期专题直播,等您解锁!

#### 第一季 直播课程 (4~6月)

纳米材料及纳米电子器件IV和CV测试 4月29日 二维材料/石墨烯及其电子器件IV和CV测试 5月15日 量子材料及超导材料电输运物性表征测试 5月29日

超快脉冲在先进的NVM测试中的应用及神经元 6月 网络测试前瞻

#### 番外篇一

测试技巧: 半导体参数测试仪使用技巧及案例集锦 7月3日

#### 第二季] 直播课程 (7~9月)

・宽禁带半导体(GaN/SiC)材料及器件测试 7月17日

·功率IGBT器件测试系统及自动化简介 7月31日

・微机电系统MEMS测试概述 8月14日

· MOSFET的准静态CV/超低频CV测试 8月28日

半导体器件可靠性HCI/NBTI测试 9月11日

· 快速上手自动化半导体参数测试系统 9月25日

- 什么是HCI

- HCI测试模型

- 如何使用4200进行HCI测试

什么是HCI

- HCI: hot carrier injection (热载流子注入) 是器件可靠性评估的一项内容。一般使用于N型MOSFET。

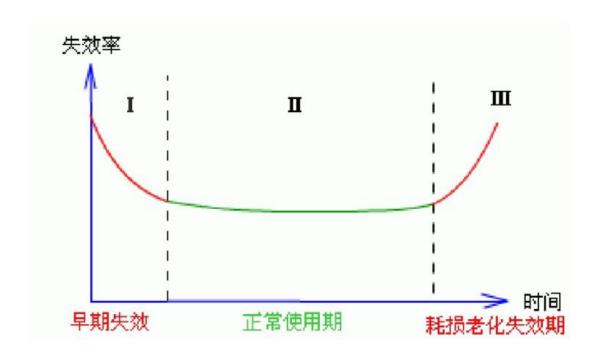

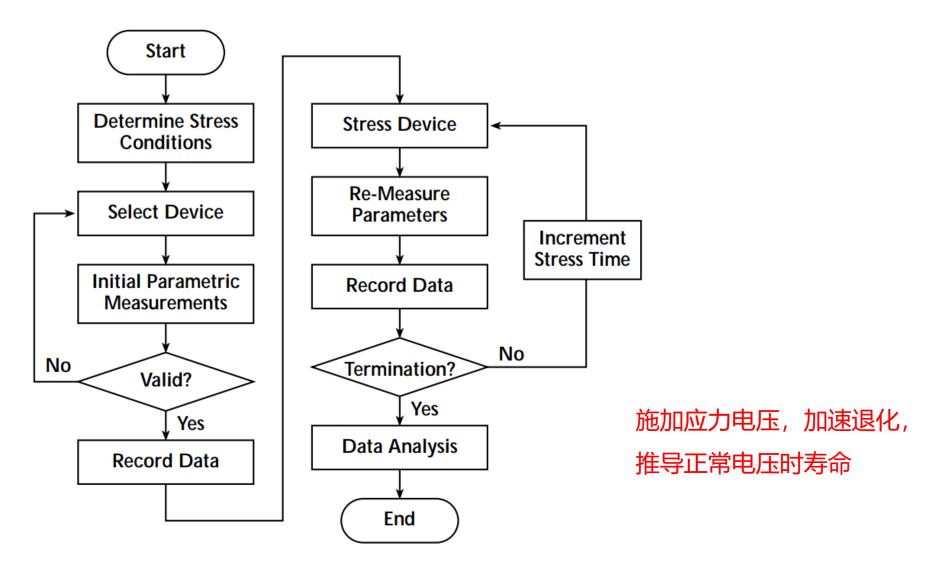

- 可靠研究:失效研究。失效分为:突然失效/**退化失效**/局部失效/全局失效。导致器件失效的影响因素有很多,包括温度/电磁场/电压等。这些失效因素,可以统称叫做"应力"。

- HCI属于是退化失效,失效应力为电压应力。它研究的是器件在正常工作电压下的工作寿命(一般要求是10年)。

什么是HCI

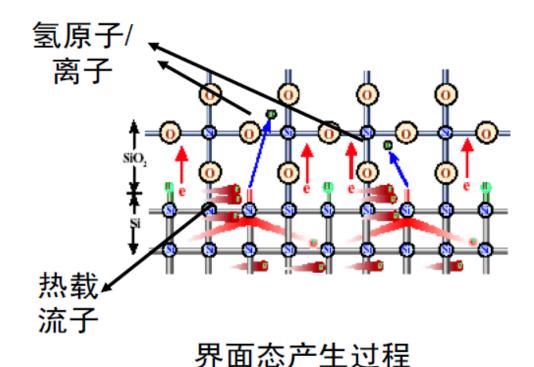

- 当电场强度大于105V/cm时,载流子从电场中获得的能量使得载流子能量大于晶格能量,这种具有高能量的载流子为热载流子。

- 当载流子的能量超过Si SiO2势垒高度时,部分高能载流子将越过Si SiO2势垒进入SiO2,在栅氧化层中产生界面陷阱和体陷阱,从而造成器件特性的退化,这种效应称为热载流子效应。

什么是HCI

#### 当"幸运电子"模型:

- (1)电子轰击打断Si-H键,造成界面态陷阱;

- (2)热载流子跨越势垒3.1eV进入氧化层形成陷阱电荷,能量更大会成为隧穿电流Ig。

- 热电子在栅电场作用下加速注入到靠近漏极的栅氧 化层,在靠近漏极的栅氧化层中形成陷阱。由于这 些陷落电子在靠近漏极处感应了较多的空穴,类似 于增加栅极电压,所以,降低了沟道中的电场,导 致器件Vth变大,Idsat减少。

HCI测试模型

#### 器件中的热载流子按照来源的不同,可以分为

- 沟道热电子(Channel Hot Electron, CHE)

- •漏极雪崩热载流子 (Drain Avalanche Hot carrier, DAHC)

- 衬底热电子(substrate hot electron, SHE)

- •二次产生热电子(Secondary Generated Hot electron, SGHE)

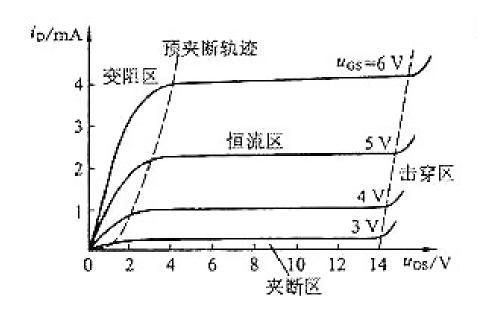

HCI测试模型

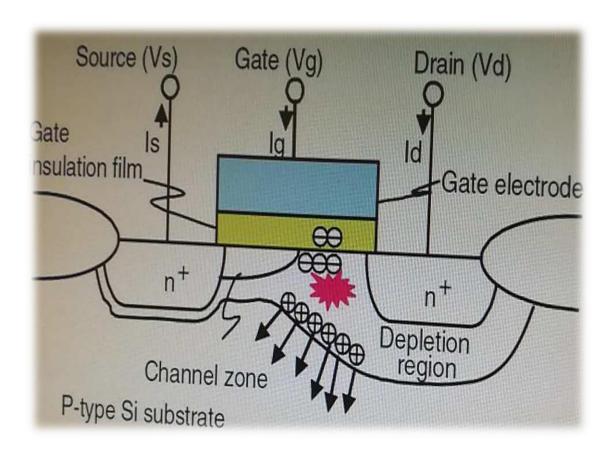

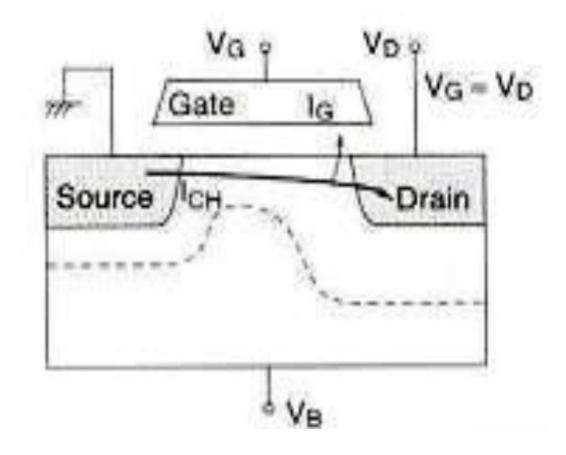

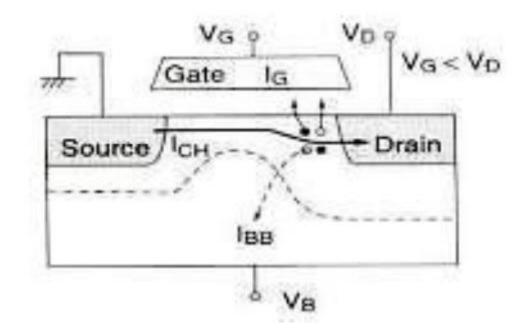

沟道热载流子(CHE),是当VG及VD都高于源端时,沟道内的载流子会在横向电场及纵向电场的共同作用下,进入栅氧层形成界面态

HCI测试模型

漏极雪崩热载流子 (DAHC) 发生在漏区边缘的强电场中。由于载流子在此电场中发生雪崩倍增,生成大量的电子空穴对。在电场的作用下,电子或空穴被扫入栅区或部分进入氧化层

HCI测试模型

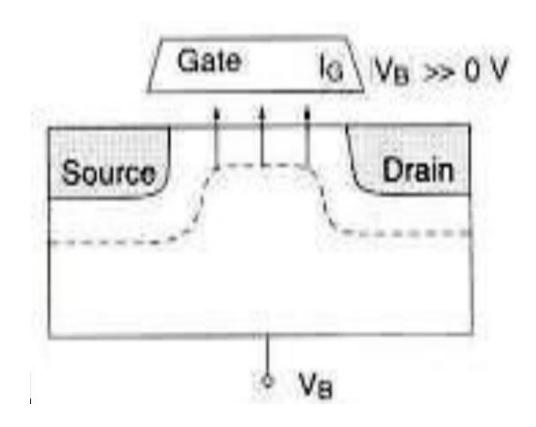

- 衬底热电子(SHE), NMOS 器件中, 当 VDS = BS,

- VGS > > VT 时,在衬底与源、漏、沟道之间有反向电流流过。衬底中的电子被耗尽区的电场拉出并加速向沟道运动,当电场足够高时,这些电子就有了足够的能量可以到达Si-SiO2 界面,并注入到SiO2中。

- 衬底热载流子注入损伤均匀

HCI测试模型

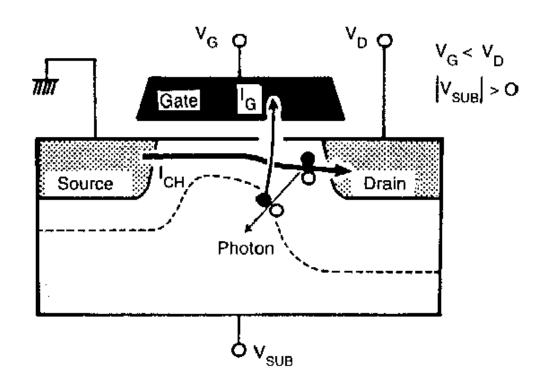

• 二次产生热电子( SGHE): 由于碰撞电离在漏极附近发射的光子,与热空穴发生二次碰撞电离,从而出现新的电子和空穴,相应的产生衬底电流和漏极电流量可以到达Si-SiO2 界面,并注入到 SiO2中。

HCI测试模型

$$I_{\text{sub}} = C_1 I_d e^{-\beta_i / E_m} \tag{1}$$

$$=C_1 I_d e^{-\varphi_i/q\lambda E_m} \tag{2}$$

$$I_g = C_2 I_d e^{-\varphi_b/q\lambda E_m} \tag{3}$$

$$I_{\text{coll}} = C_3 I_d e^{-h\nu/q\lambda E_m} \tag{4}$$

$$\Delta N_{it} = C_4 \left[ t \frac{I_d}{W} e^{-\varphi_{it}/q\lambda E_m} \right]^n \tag{5}$$

$$\tau = C_5 \frac{W}{I_d} e^{\varphi_{ii}/q\lambda E_m}. \tag{6}$$

(1) (2) 是碰撞电离方程, φi热载流子发生碰撞电离的最小能量; λ电子的平均自由程; Em最大电场 (4) hv光子能量; (5) 中Nit是界面态的产生, φit造成界面态所需的能量

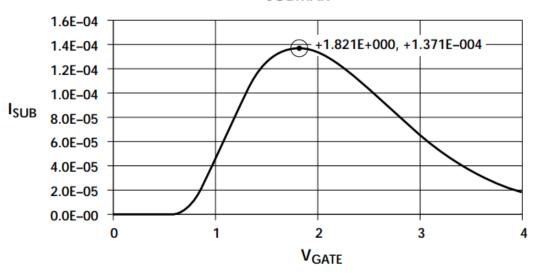

$$\tau = C / \left\{ \left( \frac{I_{sub}}{I_d} \right)^m \frac{I_d}{W} \right\}_{DC}$$

C-常数,依赖于工艺 Isub/Id-倍增因子, 反映电场强度 Id/W-沟道电子浓度 m-常数,通常2.7~3.2

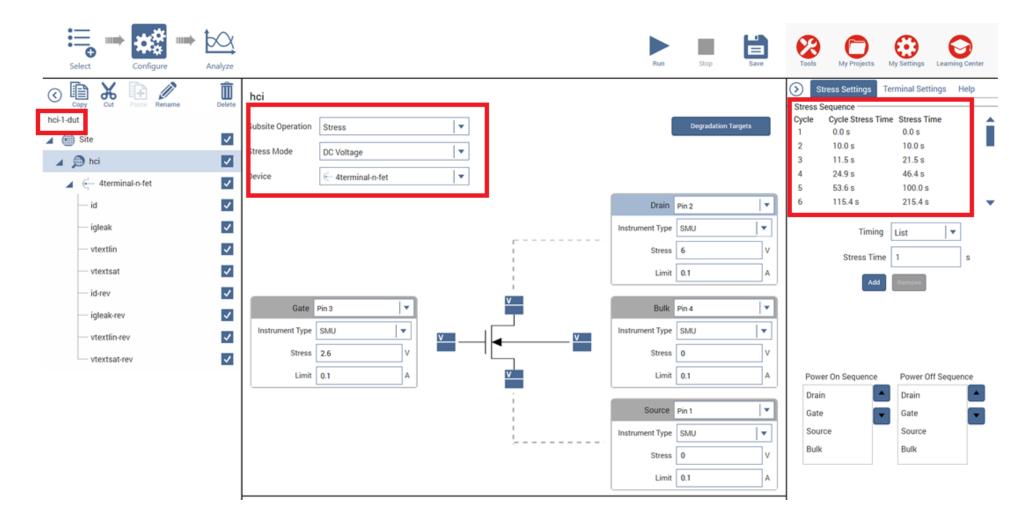

如何使用4200进行HCI测试

如何使用4200进行HCI测试

#### VGstress at I<sub>SUBMAX</sub> Characterization

Vds应力条件为击穿电压的60%-90% Vgs的应力条件为衬底电流最大处 *详情参考: JESD28*

#### 如何使用4200进行HCI测试

#### 如何使用4200进行HCI测试

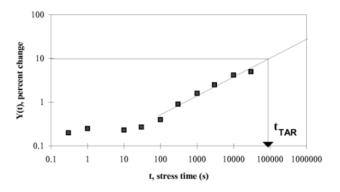

The failure time model is given by

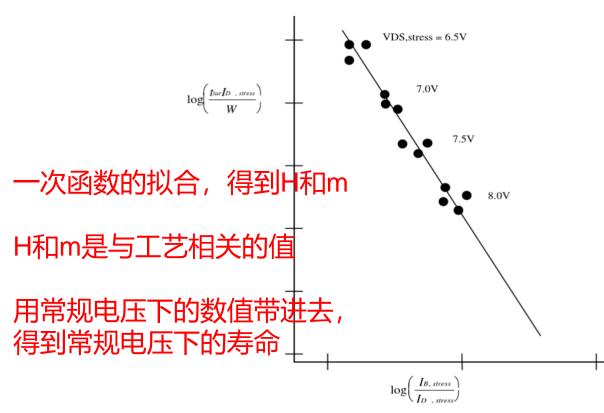

$$t_{tar}I_{D.stress} = HW \left(\frac{I_{B.stress}}{I_{D.stress}}\right)^{-m}$$

(3)

where H and m are fit parameters and W is the transistor width. If measurements are performed on transistors of equal width, then the quantity W can be combined with the fit parameter H. Rearranging Equation 3 gives:

$$\frac{t_{tar}I_{D.stress}}{W} = H \left(\frac{I_{B.stress}}{I_{D.stress}}\right)^{-1}$$

一次线性函数,

Taking the logarithm of both sides of Equation 4 yields:

$$\log\left(\frac{t_{tar}I_{D,stress}}{W}\right) = \log H - m \times \log\left(\frac{I_{B,stress}}{I_{D,stress}}\right)$$

待定变量为H和m

A linear regression analysis is performed to obtain fit parameters *H* and *m*. Figure 1 displays a plot of this relationship. According to theory, *m* should be 3, but values may vary depending on stress conditions and technology. In a stress experiment with typical stress bias voltage conditions, a moderate variation in *IB*, stress results in a large variation in failure times, tTAR. The quantity on the left hand side of Equation 5 is thus dominated by the failure times tTAR with other terms relatively constant.

Once the constants H and m are determined, the time to failure at usage condition is estimated using Equation 4 to give:

$$t_{tar,use} = HW \frac{1}{I_{D,use}} \left( \frac{I_{B,use}}{I_{D,use}} \right)^{-ns}$$

(6)

Figure 3 — Example of power law fit to hot carrier stress data

Figure 1 — Example data for substrate/drain current ratio method

- 什么是NBTI

- NBTI测试方法

- 如何使用4200进行NBTI测试

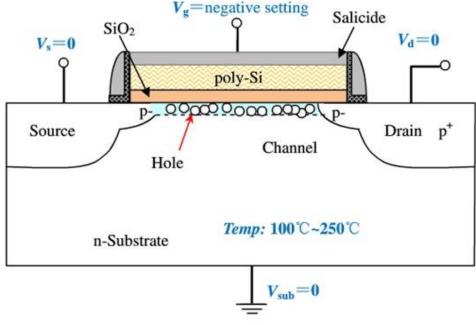

什么是NBTI测试

BTI: Negative Bias Temperature Instability (负偏压温度不稳定性) 是器件可靠性评估的一项内容。 指在高温下对PMOSFET施加负栅压而引起的一系列电学参数的退化。一般用于P型MOSFET

NBTI 效应示意图

知乎 @xianyunyeheg

什么是NBTI测试

随着器件尺寸的缩小,及新材料和结构的使用,器件的NBTI效应越来越显著,对性能的影响也更加严峻。主要原因如下:

- 1) 器件的物理尺寸不断减小,工作电压并不随着物理尺寸维度的缩小而降低,导致作用于器件上的电场应力增大。另外,器件阈值电压没有与工作电压同步进行等比例缩小,相同Vt下漏电流发生了更大比例的退化;

- 2) 随着电路集成度的提升,芯片功耗的增大导致器件工作温度升高使NBTI更严重;

- 3) MOS结构中新材料的引入(采用Hf基高k栅介质层)导致NBTI应力下介质层陷阱的产生,使NBTI愈发显著。

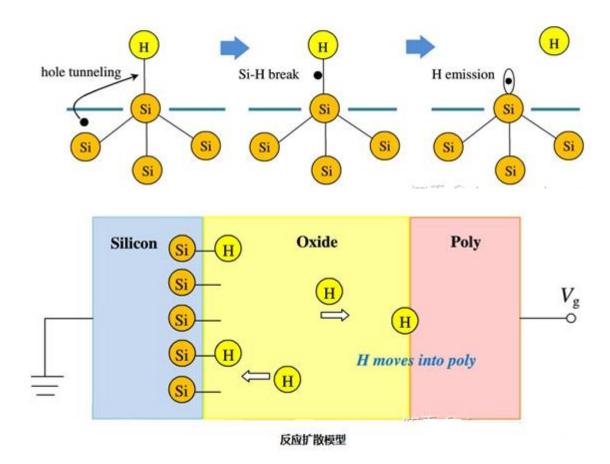

NBTI测试模型

NBTI较常使用的解释模型为反应扩散模型。

当器件的栅极处于负偏压下,器件Si/SiO2界面处经过氢钝化过程后会形成大量的Si-H键。在垂直电场作用下,产生的空穴和Si-H进行反应,使氢原子脱离,形成H,H+或者H2。

NBTI测试方法

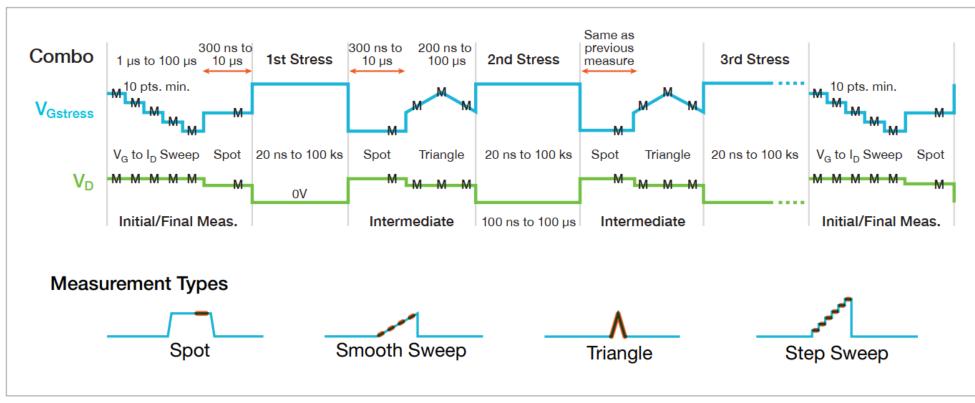

BTI: BTI造成的损伤可以恢复,而且在最初阶段恢复时间很快。为了准确测试损伤带来的影响,需要使用脉冲快速测试方法。

Ultra-fast BTI package supports spot, smooth sweep, triangle, and step sweep measurement types.

如何使用4200进行NBTI测试方法

硬件需求:

4200主机 PMU RPM

软件要求: ACS